VDHL Projects for Engineering Students.

Verilog is a hardware description language. VHDL Projects helps to integrate compiler and hardware architecture for flexible and fast data analysis. Modulator and demodulator with binary phase shift keying can framed with VHDL. Real time applications are possible through VHDL Projects. It is needed to processing FPGA devices and signal processing applications. It is also vital for analyzing much correlation detector identification. Projects of VHDL ensure varied ideas on digital circuits and signal processing based projects. All final year electronics and communication students can do VHDL projects which are more beneficial for them. Verilog language is made use by both researchers and students in research work. IC is expanded as Integrated circuits are a hardware projects on verilog need control signals and design code in a large system. Design code of verilog and its test bench is sustained by VLSI and FPGA. Our concern offers Verilog based projects for ECE students. It is used by PHD scholars to analyze performance of new system.

Components of VHDL Projects.

Architecture: Internal implementation of module as per instructed by corresponding applications can be implemented through architecture. The hierarchical model is varied in VHDl architecture due to its base on topology. They are:

- Sequential Behavioral Description.

- Concurrent Behavioral Description.

Package: A set of components, functions and data types form a package. Two entirely varied types of processing are performed by VHDL package they are:-

- Package Body.

- Package Declaration.

Configuration Declaration: Different design units with unique system description make use of configuration declaration. Structural and behavioral models are the types of system description architecture.

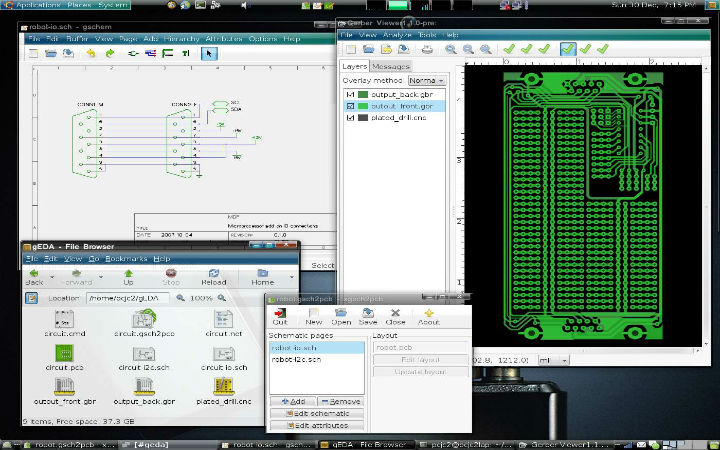

Entity Declaration: Certain entities and their interface function is specified through entity declaration. Information regarding any application is understood through various symbols through schematic drawings. These signals and surroundings needed for any certain communication is known as ports.

Features of VHDL:

- Powerful Language.

- Support Multi Valued Logic.

- Supports Sequential Statement.

- Supports Vendor Defined Applications.

- Supports for Test and Simulation.

- Strongly Typed Language.

- Complexity is low.

- Verilog is a case sensitive language.

- Testing can be done by different test bench model.

- Verilog has ability to mix different levels of abstract freely.

- Easy and freely handle.

- Single language can provide different aspect such as design, testing and verification.

Verilog HDL Simulators:

- Modelsim.

- Verilog-XL

- VCS

- NC-Verilog.

Abstraction Levels in VHDL Projects.

Structural Level: Modeling of entity as per in connected statement are implemented through structure level abstraction.

Behavioral Level: Any specific entity and the set of statement are analyzed through this level and its behavior is listed out in a specific order.

Data Flow Level: Flow of data by means of entity which is revealed by concurrent signals and assignments is brought through data flow level.

Register Transfer Level: Features of various circuits are specified by its operations and data transfer among registers through register transfer level. An explicit clock is used to fix a time at which the operations should take place.

Switch Level: It is abstractions lowest level. Storage nodes, switches and interconnection among these are established by switch level.

Algorithm Level: It is otherwise known as behavioral level as it contains a sequential procedure. These procedure should be performed in the mentioned order. To define structure algorithm level blocks various tasks, always, functions and initial.

Gate Level: This abstraction is defined features of logic system and their timing properties. Only discrete signals are used in gate level process. Synthesis tools are needed for gate level code.

Interface components of Verilog Projects:

By using hardware description language efficient VLSI design method with various components are interfaced. Such often used hardware inferences are as follows:-

Latches: If a variable doesn’t have any statement branch it is inferred with latch. It is also used for improving readability of code in a statement. It is quiet hard to use case statement to specify latch enabled signal.

Registers, Flip-Flops, Counters: Positive edge or negative edge is used to infer register in a clock of an event. In other case active and reset condition are inferred by flip flops and counters.

Multiplexers: This is inferred as it allots a single variable to various variables in every branch. Case statement should be inferred to improve code readability.

Adders/ Subtracters: Only the operand width can determine subtracter and adder operators’ inference.

Tristate Buffers: It infers with conditional operators assigned variables in case statement.

Important Packages in VHDL Projects.

- TEXTIO.

- STD-LOGIC-ARITH.

- NUMERIC-STD.

- STANDARD.

- STD-LOGIC-1164.

Benefits of VHDL:

- Productivity of application can be improved.

- Automatic synthesis and test generation are available.

- Portable data availability.

- Functionality can be spreaded from independence.

- Simulation is done early and very fast.

- Feedback is also available.

- Automate mapping of high level description of technology.

- Verilog HDL can provide greater flexibility to reuse.

- Different level of test bench can be used for various applications and vendors.

- Top down methodology can be implemented by synthesis.

- Problems in synthesis can be finding earlier.

Applications of VHDL Projects.

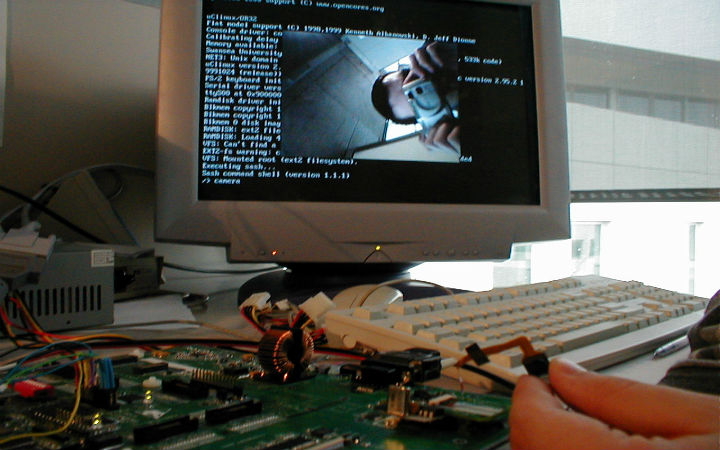

- To simulate electronic circuit modeling.

- Most of the FPGA implementation can be processed by using VHDL.

- VHDL language can be applied into micro sensor monitoring.

- Magnetic field sensors can be demonstrated using VHDL.

- Automatic electronic control devices.

- Large program synthesis needed.

- Fingerprint recognition.

- Gabor filter implementation in matlab

- FPGA implementation system.

I was not sure about the concepts clearly before coming to you. your staffs provided me a training and projects concept in a detailed way. Excellent training.

Project center provide a comfort environment to discuss about a project ideas.motivated and support to my projects in an effective way.

I had a great platform to learn about new technologies and working under experienced team members. They follow a unique methodology to develop a project.

Your staffs involvement towards project is awesome.Thanks a lot for giving me a great opportunity.